Product Summary

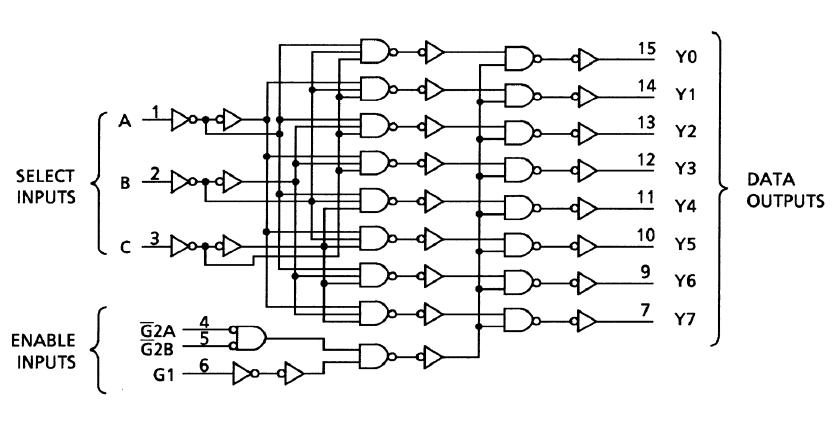

The 74HC238AP is a high speed CMOS 3-to-8 decoder fabricated with silicon gate C2MOS technology. It achieves the high speed operation similar to equivalent LSTTL while maintaining the CMOS low power dissipation. When the 74HC238AP is enabled, 3 Binary Select inputs (A, B and C) determine which one of the outputs (Y0-Y7) will go high. When enable input G1 is held low or either G2A or G2B is held high, decoding function is inhibited and all the outputs go low. G1, G2A, and G2B inputs are provided ease cascade connection and for use as an adress decoder for memory systems.

Parametrics

74HC238AP absolute maximum ratings: (1)Supply voltage range, VCC: -0.5 to 7 V; (2)DC input voltage, VIN: -0.5 to VCC +0.5 V; (3)DC output voltage, VOUT: .0.5 to VCC +0.5 V; (4)Input diode current, IIK: ±20 mA; (5)Output diode current, IOK: ±20 mA; (6)DC output current, IOUT: ±25 mA; (7)DC VCC/ground current, ICC: ±50 mA; (8)Power dissipation, PD: 500 (DIP)/180 (SOP) mW; (9)Storage temperature, Tstg: -65 to 150℃.

Features

74HC238AP features: (1)High speed: tpd = 14 ns (typ.) at VCC = 5 V; (2)Low power dissipation: ICC = 4 μA (max) at Ta = 25℃; (3)High noise immunity: VNIH = VNIL = 28% VCC (min); (4)Output drive capability: 10 LSTTL loads; (5)Symmetrical output impedance: |IOH| = IOL = 4 mA (min); (6)Balanced propagation delays: tpLH ≈ tpHL; (7)Wide operating voltage range: VCC (opr) = 2 to 6 V; (8)Pin and function compatible with 74LS238.

Diagrams

|

74HC |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT02 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT03 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT10 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT107 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

74HC/HCT109 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(Hong Kong)

(Hong Kong)