Product Summary

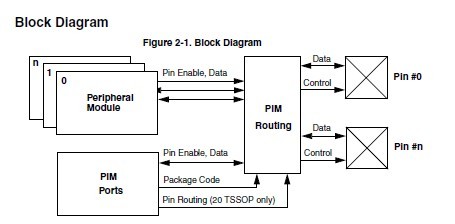

The s9s12g128mlh is an optimized, automotive, 16-bit microcontroller product line focused on low-cost, high-performance, and low pin-count. The s9s12g128mlh delivers all the advantages and efficiencies of a 16-bit MCU while retaining the low cost, power consumption, EMC, and code-size efficiency advantages currently enjoyed by users of Freescales existing 8-bit and 16-bit MCU families. The s9s12g128mlh runs 16-bit wide accesses without wait states for all peripherals and memories. The s9s12g128mlh is available in 100-pin LQFP, 64-pin LQFP, 48-pin LQFP/QFN, 32-pin LQFP and 20-pin TSSOP package options and aims to maximize the amount of functionality especially for the lower pin count packages. In addition to the I/O ports available in each module, further I/O ports are available with interrupt capability allowing wake-up from stop or wait modes.

Parametrics

s9s12g128mlh absolute maximum ratings: (1)I/O, regulator and analog supply voltage VDD35: -0.3 to 6.0 V; (2)Digital I/O input voltage VIN: -0.3 to 6.0 V; (3)Analog reference VRH: -0.3 to 6.0 V; (4)EXTAL, XTAL VILV: -0.3 to 2.16 V; (5)All digital I/O pins are internally clamped to VSSX and VDDX, or VSSA and VDDA. ID: -25 to +25 mA; (6)Instantaneous maximum current Single pin limit for EXTAL, XTAL IDL: -25 to +25 mA; (7)Maximum current Single pin limit for power supply pins IDV: -60 to +60 mA; (8)Storage temperature range (M, V, C, and W temperature range)Tstg: -65 to 155°C.

Features

s9s12g128mlh features: (1)Up to one multi-scalable controller area network (MSCAN)module (supporting CAN protocol; (2)2.0A/B); (3)On-chip voltage regulator (VREG)for regulation of input supply and all internal voltages; (4)Autonomous periodic interrupt (API); (5)Precision fixed voltage reference for ADC conversions; (6)Optional reference voltage attenuator module to increase ADC accuracy; (7)Full 16-bit data paths supports efficient arithmetic operation and high-speed math execution; (8)Includes many single-byte instructions. This allows much more efficient use of ROM space; (9)Data registers and data direction registers for ports A, B, C, D, E, T, S, M, P, J and AD when used as general-purpose I/O; (10)Control registers to enable/disable pull devices and select pullups/pulldowns on ports T, S, M, P, J and AD on per-pin basis; (11)Single control register to enable/disable pull devices on ports A, B, C, D and E, on per-port basis and on BKGD pin; (12)Control registers to enable/disable open-drain (wired-or)mode on ports S and M.

Diagrams

(Hong Kong)

(Hong Kong)