Product Summary

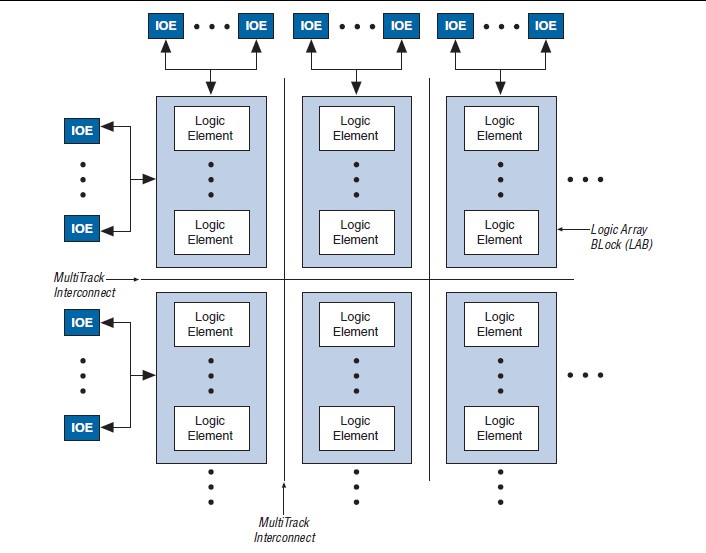

The 5M160ZE64C5N is a low cost and low power CPLD. The 5M160ZE64C5N contains a two-dimensional row- and column-based architecture to implement custom logic. Row and column interconnects provide signal interconnects between the logic array blocks (LABs). Each LAB in the logic array contains 10 logic elements (LEs). An LE is a small unit of logic that provides efficient implementation of user logic functions. LABs are grouped into rows and columns across the 5M160ZE64C5N. The MultiTrack interconnect provides fast granular timing delays between LABs. The fast routing between LEs provides minimum timing delay for added levels of logic versus globally routed interconnect structures.

Parametrics

5M160ZE64C5N absolute maximum ratings: (1)Internal supply voltage. With respect to ground: –0.5 to 2.4 V; (2)I/O supply voltage: –0.5 to 4.6 V; (3)DC input voltage: –0.5 to 4.6 V; (4)DC output current, per pin: –25 to 25 mA; (5)Storage temperature. No bias: –65 to 150 °C; (6)Ambient temperature. Under bias (3): –65 to 135 °C; (7)Junction temperature. TQFP and BGA packages under bias: 135 °C.

Features

5M160ZE64C5N features: (1)Low-cost, low-power, and non-volatile CPLD architecture; (2)Instant-on (0.5 ms or less)configuration time; (3)Standby current as low as 25 μA and fast power-down/reset operation; (4)Fast propagation delay and clock-to-output times; (5)Internal oscillator; (6)Emulated RSDS output support with a data rate of up to 200 Mbps; (7)Emulated LVDS output support with a data rate of up to 304 Mbps; (8)Four global clocks with two clocks available per logic array block (LAB); (9)User flash memory block up to 8 Kbits for non-volatile storage with up to 1000 read/write cycles; (10)Single 1.8-V external supply for device core; (11)MultiVolt I/O interface supporting 3.3-V, 2.5-V, 1.8-V, 1.5-V, and 1.2-V logic levels; (12)Bus-friendly architecture including programmable slew rate, drive strength, bus-hold, and programmable pull-up resistors; (13)Schmitt triggers enabling noise tolerant inputs (programmable per pin).

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

5M160ZE64C5N |

|

IC MAX V CPLD 160 LE 64-EQFP |

Data Sheet |

|

|

||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|

5M160ZE64C4N |

|

IC MAX V CPLD 160 LE 64-EQFP |

Data Sheet |

|

|

||||||

|

5M160ZE64C5N |

|

IC MAX V CPLD 160 LE 64-EQFP |

Data Sheet |

|

|

||||||

|

5M160ZE64I5N |

|

IC MAX V CPLD 160 LE 64-EQFP |

Data Sheet |

|

|

||||||

|

5M160ZM100C4N |

|

IC MAX V CPLD 160 LE 100-MBGA |

Data Sheet |

|

|

||||||

|

5M160ZM100C5N |

|

IC MAX V CPLD 160 LE 100-MBGA |

Data Sheet |

|

|

||||||

|

5M160ZM100I5N |

|

IC MAX V CPLD 160 LE 100-MBGA |

Data Sheet |

|

|

||||||

(Hong Kong)

(Hong Kong)