Product Summary

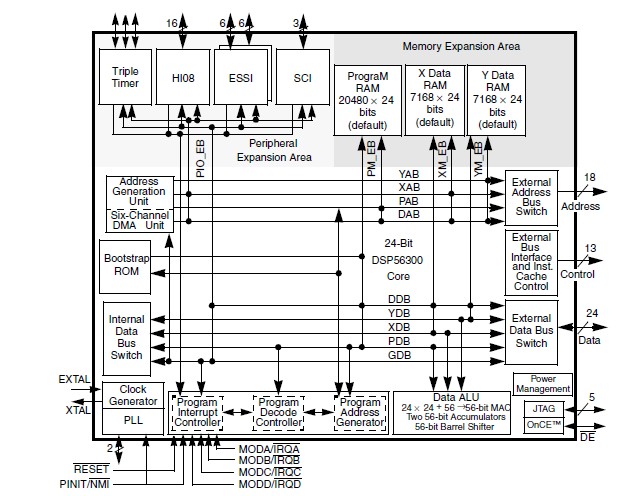

The XC56301PW803F48S is a programmable CMOS DSP. The XC56301PW803F48S includes a barrel shifter, 24-bit addressing, an instruction cache, and direct memory access (DMA). The XC56301PW803F48S offers 100 MMACS at 3.0–3.6 V using an internal 100 MHz clock. The large internal memory is ideal for wireless infrastructure and wireless local-loop applications. The XC56301PW803F48S offers a new level of performance in speed and power provided by its rich instruction set and low-power dissipation, thus enabling a new generation of wireless, multimedia, and telecommunications products.

Parametrics

XC56301PW803F48S absolute maximum ratings: (1)Supply Voltage VCC: −0.3 to +4.0 V; (2)All input voltages excluding inputs VIN GND: − 0.3 to VCC + 0.3 V; (3)All input voltages2 VIN5 GND: − 0.3 to 5.5 V; (4)Current drain per pin excluding VCC and GND I: 10 mA; (5)Operating temperature range TJ: −40 to +100 °C; (6)Storage temperature TSTG: −55 to +150 °C.

Features

XC56301PW803F48S features: (1)Serial communications interface (SCI)with baud rate generator; (2)Triple timer module; (3)Up to thirty-four programmable general-purpose input/output (GPIO)pins, depending on which peripherals are enabled; (4)Phase-lock loop (PLL)allows change of low-power divide factor (DF)without loss of lock and output clock with skew elimination; (5)Hardware debugging support including On-Chip Emulation (OnCE)module, Joint Test Action Group (JTAG)test access port (TAP); (6)External memory expansion port; (7)Chip select logic for glueless interface to static random access memory (SRAMs); (8)Internal DRAM Controller for glueless interface to dynamic random access memory (DRAMs); (9)144-pin TQFP package in lead-free or lead-bearing versions; (10)196-pin molded array plastic-ball grid array (MAP-BGA)package in lead-free or lead-bearing versions.

Diagrams

(Hong Kong)

(Hong Kong)