Product Summary

The hyi18t512160b2f-3s is a high-speed Double-Data-Rate-Two CMOS Synchronous DRAM device, containing 1,073,741,824 bits and internally configured as anoctal quadbank DRAM. The 1-Gbit device is organized as either 32 Mbit × 4 I/O × 8 banks, 16 Mbit × 8 I/O × 8 banks or 8 Mbit × 16 I/O × 8 banks chip. The hyi18t512160b2f-3s achieves high speed transfer rates starting at 400 Mb/sec/pin for general applications.

Parametrics

HYI18T512160B2F-3S absolute maximum ratings: (1)Voltage on VDD pin relative to VSS: –1.0 to +2.3 V; (2)Voltage on VDDQ pin relative to VSS: –0.5 to +2.3 V; (3)Voltage on VDDL pin relative to VSS: –0.5 to +2.3 V; (4)Voltage on any pin relative to VSS: –0.5 to +2.3 V; (5)Storage Temperature: –55 to +100 ℃.

Features

HYI18T512160B2F-3S features: (1)Posted CAS with additive latency,; (2)Write latency = read latency - 1,; (3)Normal and weak strength data-output driver,; (4)Off-Chip Driver (OCD) impedance adjustment; (5)On-Die Termination (ODT).

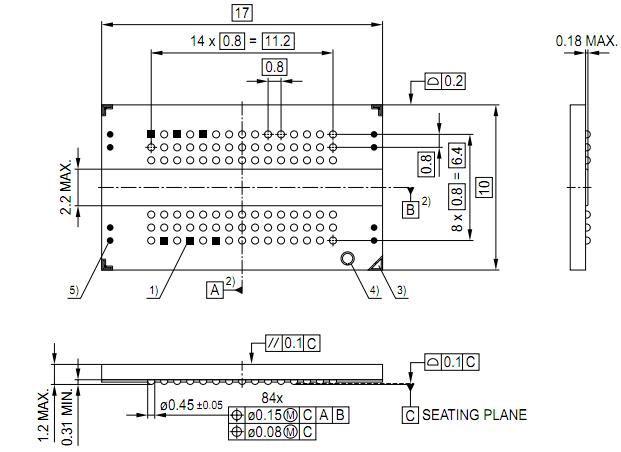

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

HYI18T512160B2F-3S |

Other |

|

Data Sheet |

Negotiable |

|

||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|

HYI18T1G160BC-5 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYI18T1G160BF-3.7 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYI18T1G160C2C-2.5 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYI18T1G160C2C-3.7 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYI18T1G160C2C-3S |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

HYI18T1G160C2F-2.5 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(Hong Kong)

(Hong Kong)